# Proceedings of the International Conference on Accelerator and Large Experimental Physics Control Systems

November 11-15, 1991 KEK, Tsukuba, Japan

### **FOREWORD**

International Conference on Accelerators and Large Experimental Physics Control Systems (ICALEPCS'91) was held on November 11 - 15, 1991 at KEK, Tsukuba, Japan. This was the first conference in this series held in Asia. It was a great pleasure for the organizers of the conference that more than 240 participated. Among them we were delighted to see large delegates from countires and institutions such as Russia, China, Korea, India, SRRC in Hsinchu, etc. from which very few had participated in the former conferences. This reflects the fact that the society has come to its maturity, to which the continuing effort by EPCS(Interdivisional Group on Experimental Physics Control Systems under European Physical Society) has contributed greatly.

The maturity was also demonstrated by a naming of the "standard model" of control systems which we heard during the conference. Also, in the conference, discussion was held on prospects of making a generic tool-kit of control system on the basis of world-wide collaboration. Of course, we are far from this goal; however, it is sure that we glimpsed our future during the conference.

Shin-ichi Kurokawa Chairperson of ICALEPCS'91

Tadahiko Katoh

Chairperson of Local Organizing Committee

小成五名

### LIST OF INTERNATIONAL SCIENTIFIC ADVISORY COMMITTEE MEMBERS

BARTON, Donald S. (BNL)

BUSSE, Winffied (HMI)

DANEELS, Axel Jean (CERN)

DOHAN, Don A. (SSCL)

GURD, David P. (SSCL)

JAN, Gwo-Jen (SRRC)

KIMURA, Toyoaki (JAERI-Naka)

KUPER, Edward (INP-Novosibirsk)

LIU, Shi-Yao (IHEP-Beijing)

LUDGATE, George Arthur (TRIUMF)

MÜLLER, Klaus-Dieter (KFA)

NISHIMURA, Hiroshi (LBL)

PETERS, Franz (DESY)

SCHALLER, Stuart (LANL)

WADA, Takeshi (RIKEN)

BLUMER, Thomas (PSI)

CLOUT, Peter Norman (VISTA)

DASGUPTA, Subrata (VECC)

DUNAITSEV, Anatoly F. (IHEP-Serpukhov)

HUMPHREY, John (Rusty)(SLAC)

KATOH, Tadahiko (KEK)

KUIPER, Berend (CERN)

KUROKAWA, Shin-ichi (KEK) - Chairperson

LUCAS, Peter Wayne (Fermilab)

LUONG, Tam T. (GANIL)

NAVRATIL, Jiri (CTU)

OWEN, Edward Charles (Daresbury)

RAUSCH, Raymond (CERN)

STEINER, Rudolf (GSI)

WON, Sangchul (PLS)

### LIST OF LOCAL ORGANIZING COMMITTEE MEMBERS

KATOH, Tadahiko (KEK) - Chairperson KOHNO, Toshiyuki (NIRS) MORITA, Koh-Ichiro (NAO-NRO) OGATA, Hiroshi (RCNP) PAK, Cheol On (KEK) URAKAWA, Junji (KEK) WATANABE, Shin-ichi (INS) KIMURA, Toyoaki (JAERI-Naka) KUROKAWA, Shin-ichi (KEK) NAKAHARA, Kazuo (KEK) OYAMADA, Masayuki (LNS) TAKEDA, Shigeru (KEK) WADA, Takeshi (RIKEN)

Organized by:

KEK, National Laboratory for High Energy Physics

Supported by:

European Physical Society

IEEE Nulcear and Plasma Sciences Society

Japan Physical Society

Sponsored by:

Tsukuba EXPO '85 Memorial Foundation

Foundation for High Energy Accelerator Science

# Contents

| Preface                                                                                                                             | į   |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| Foreword                                                                                                                            | iii |

| Committees                                                                                                                          | iv  |

| Contents                                                                                                                            | V   |

| n.                                                                                                                                  |     |

| Papers                                                                                                                              | 1   |

| SOISRAOI – A Users View of the SPS and LEP Control Systems                                                                          | 1   |

| S01SRA02 – Experience Controlling the LAMPF-PSR Accelerator Complex                                                                 | 7   |

| SOISRAO3 – Status Report on the Advanced Light Source Control System                                                                | 11  |

| S01SRA04 – Lessons from the SLC for Future LC Control Systems                                                                       | 14  |

| S01SRA05 – Process Control for the Vivitron: the Generator Test Set-up                                                              | 19  |

| S01SRA06 – Recent Developments of the ALPI Control System                                                                           | 23  |

| S01SRA07 – The GSI Control System                                                                                                   | 27  |

| SOISRAO8 – VME Applications to the Daresbury SRS Control System                                                                     | 31  |

| S01SRA09 – Accelerator Control Systems in China                                                                                     | 35  |

| S01SRA10 – HESYRL Control System Status                                                                                             | 40  |

| SO1SRA11 – The Control System of HIRFL                                                                                              | 44  |

| SO1SRA12 – Control System for a Heavy-Ion Accelerator Complex K4 - K10                                                              | 47  |

| SO2SRU01 – Future Directions in Controlling the LAMPF-PSR Accelerator Complex at Los Alamos National Laboratory                     | 50  |

| SO2SRUO2 – Common Control System for the CERN Accelerators                                                                          | 54  |

| SO2SRU03 – New Control Architecture for the SPS Accelerator at CERN                                                                 | 59  |

| SO2SRU04 – The Next Generation Control System of GANIL                                                                              | 65  |

| S02SRU05 – Replacement of the ISIS Control System                                                                                   | 71  |

| SO2SRU06 – Upgrading the Control System for the Accelerators at The Svedberg Laboratory                                             | 78  |

| S02SRU07 – Upgrading the BEPC Control System                                                                                        | 82  |

| SO2SRU08 – The Rejuvenation of TRISTAN Control System                                                                               | 85  |

| S02SRU09 – Upgrade Plan for the Control System of the KEK e <sup>+</sup> /e <sup>-</sup> Linac                                      | 89  |

| SO2SRU10 – The New Control System for TARN-2                                                                                        | 93  |

| SO2SRU11 – A New Architecture for Fermilab's Cryogenic Control System                                                               | 96  |

| SO3SRD01 – Controls for the CERN Large Hadron Collider (LHC)                                                                        | 100 |

| SO3SRD02 – A Performance Requirements Analysis of the SSC Control System                                                            | 105 |

| SO3SRDO3 – The Computer Control System for the CESR B Factory                                                                       | 110 |

| SO3SRD04 – Standards and the Design of the Advanced Photon Source Control System                                                    | 116 |

| S03SRD05 – The ESRF Control System; Status and Highlights                                                                           | 121 |

| <code>SO3SRD06</code> – Centralized Multiprocessor Control System for the Frascati Storage Rings <code>DA<math>\Phi</math>NE</code> | 128 |

| SO3SRD07 – The Operator View of the Superconducting at LNS Catania                                                                  | 131 |

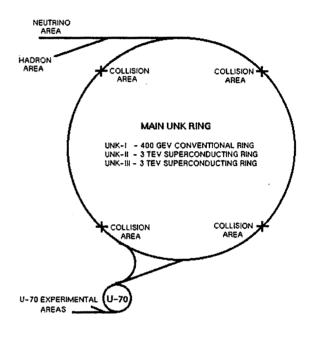

| SO3SRD08 – The UNK Control System                                                                                                   | 134 |

| SO3SRD09 – Moscow University Race-Track Microtron Control System: Ideas and Development                                             | 140 |

| SO3SRD10 – Present Status of Control System at the SRRC                                                                             | 143 |

| SO3SRD11 – Status Report on Control System Development for PLS                                                                      | 147 |

| SO3SRD12 – Design of SPring-8 Control System                                                                                        | 151 |

| SO3SRD13 – Design of a Control System of the Linac for SPring-8                                                                     | 154 |

| SO3SRD14 – Control System for HIMAC Synchrotron                                                                                     | 156 |

| SO4SRSO1 – Digital Control of the Superconducting Cavities for the LEP Energy Upgrade                                               | 159 |

| SO4SRSO2 – A PC Based Control System for the CERN ISOLDE Separators                                                                 | 162 |

| SO4SRSO3 – Status of the Control and Beam Diagnostic Systems of the CRYRING Project                                                 | 167 |

| SO4SRSO4 – Magnet Test Facility Control System for Superconducting Magnets of UNK                                                   | 171 |

| SO4SRSO5 – Beam Extraction Controlsystems of the Fast-Cycling Synchrotron                                                           | 174 |

| SO4SRSO6 – Instrumentation & Control System For PLS-IM-T 60 MeV LINAC                                                               | 177 |

| SO4SRS07 – Multi-Microprocessor Control of the Main Ring Magnet Power Supply of the 12 GeV KEK Proton Synchrotron                   | 180 |

| SO4SRSO8 – VME Computer Monitoring System of KEK-PS Fast Pulsed Magnet Currents and Beam Intensities                                | 184 |

| SO4SRSO9 – Magnet Power Supply and Beam Line Control for a Secondary Beam Line K6                                                   | 188 |

| SO4SRS10 – Specific Beam Delivery System of Medical Accelerator HIMAC                                                               | 192 |

Contents

| Appendices           |    |  |  |  |

|----------------------|----|--|--|--|

| List of Authors      | 19 |  |  |  |

| List of Institutes   | 19 |  |  |  |

| List of Participants | 20 |  |  |  |

vi Contents

# A USERS VIEW OF THE SPS AND LEP CONTROL SYSTEMS

### R. Bailey **CERN** CH-1211 Geneva 23, Switzerland

### Abstract

Every accelerator has a control system; at present the SPS has two, both of which are needed to run the machine. Consequently a user of the SPS / LEP complex has to be concurrently familiar with three control systems. While this situation brings problems it allows, even forces, comparison between the different systems, which in turn enriches the user viewpoint.

This paper assesses the SPS and LEP control systems from the point of view of the user, who may be an equipment specialist, operator, accelerator physicist or combinations thereof.

#### 1. Introduction – what the accelerators do

Exploitation of the two large accelerators at CERN is a varied business. For the SPS in 1991 this amounts to running as a fixed target machine for over half the year, providing either protons (during 21 weeks) or sulphur ions (during 6 weeks) to the physics community. In conjunction with this the SPS acts as an injector to LEP, providing leptons in an interleaved repetitive supercycle. Furthermore about 15% of the fixed target running time is given over to machine development periods, when the SPS is required to run in some non-standard way, mostly as a testbed for the LHC. Finally, the SPS is also used in the other major mode of operation, as a proton-antiproton collider, for about 5 weeks.

In parallel with all of the 27 weeks of SPS fixed target running, LEP is taking beam either for Z<sup>o</sup> production or for a substantial machine development program, the latter amounting to about 30% of the total LEP running time.

For both machines, although mostly for LEP, installation and testing of new equipment is carried out throughout the year.

This diversity of operations and machine improvement is carried out from a common central control room, with the same teams being responsible for both the SPS and LEP. In particular, one group run the SPS in a variety of modes of operation throughout the year as well as running LEP. This means that these personnel have to be familiar with the different control systems used to interact with the accelerators. The same is true of the personnel responsible for equipment commissioning.

### 2. Overview of control systems available

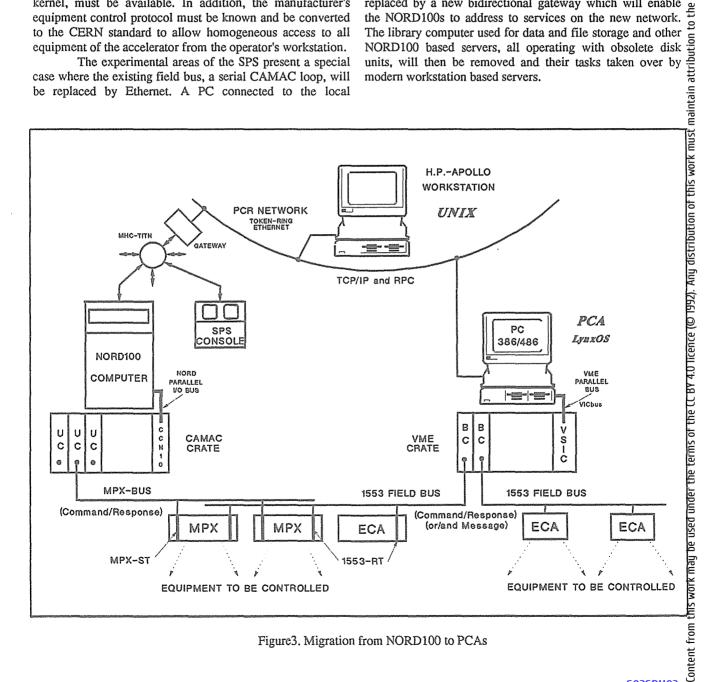

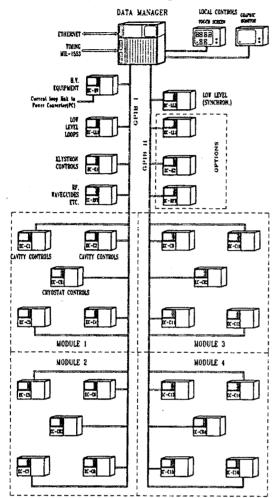

From 1975 the SPS has been controlled, either exclusively or partially, via a system based on Norsk Data ND100 computers connected in a TITN star configuration [1]. The computers run SINTRON and the programmers are provided with the NODAL interpreter, libraries of graphics primitives and data modules and a means of calling FORTRAN executables [2].

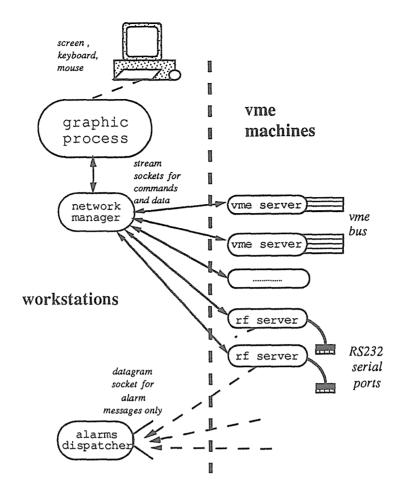

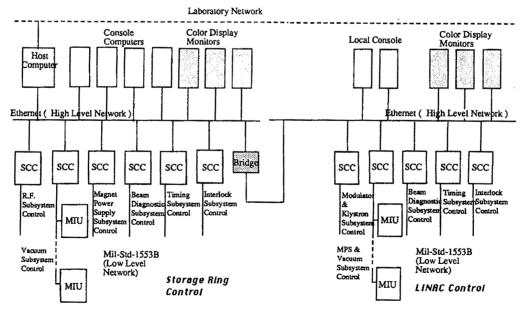

From 1985 the major new requirement for SPS to provide beams to LEP meant a complete rewrite of the applications software. This was undertaken in a UNIX environment on an Apollo network, with C as the main programming language and Apollo-Dialog for the user interface. In the first instance access to the hardware was via a gateway into the existing TITN system. More recently the possibility exists to access some equipment completely independently from the TITN system, using the same overall Token Ring architecture as for LEP (see

Presently the SPS is run using a mixture of purely TITN (30%), Apollo via the gateway into TITN (50%), and purely Apollo Token Ring applications (20%) (see figure 1).

LEP applications also run on an Apollo network, with C as the main programming language and Apollo-Dialog for the user interface. All the Apollos are connected on a control room Token Ring, with communications out into the field through a bridge to a machine Token Ring running around the accelerator [3]. At several points around the ring there is a further bridge or gateway into either a regional Token Ring or an Ethernet network. Connected to these local area networks is a variety of configurations, allowing access into the hardware via several different equipment control assemblies, mostly using the MIL-1553-B standard (see figure 1).

Content from this work may be used under the S01SRA01

must maintain attribution to the author(s), title of the work, publisher, and DOI

work

BY 4.0 licence (© 1992). Any distribution of this

$\overline{z}$

the

terms of

Figure 1 Logical schematic of the networks

2

## 3. Different types of user

The control systems of SPS and LEP are used at different times by a variety of different personnel. These largely divide into three categories; operators, accelerator physicists and equipment specialists, each of whom have somewhat different requirements for the control system. These requirements are not only for the underlying architecture (network, operating system etc), but also for the applications that run on top of it. In other words, the user here is seen as the person who runs the applications programs, rather than the person who writes them.

All types of user of course need reliable network communications, with good diagnostics when things go wrong. An adequate speed across the network from console to equipment is also generally required.

### 3.1 Equipment specialists

Equipment specialists need to access a diversity of accelerator hardware, setting and reading a multitude of parameters that are not of interest to other users of the control system. In many cases they also need to do this locally, in order to closely monitor the effects on their equipment. This means that they need to run specific programs both in the central control room and in the field, the latter requiring local console facilities. They may well want to run locally when the network is down. Most of these programs are written by the person who will run them, or at least by a close colleague, and as such the reliability of the application is not of great importance.

In many cases the amount of equipment accessed is far more than during normal operations, in order to thoroughly test a system, for example. For this reason the speed can be of prime importance to the equipment groups.

Key requirements;

local console facilities execution speed

### 3.2 Operators

Operators rarely work on individual pieces of equipment, but rather on combinations of accelerator systems or even on the accelerator as a whole. In performing this work they prefer to see a high level of standardisation across the different applications and across the different accelerators. The applications also need to be easy to use, with the operator being presented with all the

information that he needs but not swamped by auxiliary data that he rarely uses. Online documentation is a big help, particularly when the applications are new.

Since many tasks have to be performed at the right time in a sequence, the applications that perform them need to be highly reliable. Since operations is a long and repetitive process, it is essential that the speed of execution of programs is adequate, which generally means completion of the task in a matter of seconds. Good error reporting is also very important.

Key requirements;

ease of use stability standardisation execution speed error reporting

### 3.3 Accelerator physicists

Accelerator physicists have essentially the same requirements as the operators, except for the important addition of flexibility to allow new, non-standard applications to be used. Indeed since machine development periods usually involve doing several unusual things, standardisation and error reporting are not so important.

Key requirements;

flexibilty

ease of use stability execution speed

### 4. Comparison of the different control systems

Table 1 summarises the results discussed in more detail here.

In all three cases the speed and reliability of the network is adequate. However when there is a problem, it is much easier to pinpoint on the TITN system than on the Token Rings, which have become extremely complex.

Local facilities are also better on the TITN, where much of the equipment data is stored locally rather than in a central database.

Table 1 Comparison of observations

|           | ruoid r                            | 01 0000                   | - rations |     |  |

|-----------|------------------------------------|---------------------------|-----------|-----|--|

| IOQ pue   |                                    | SPS old                   | SPS new   | LEP |  |

| isher, a  | <u>Network</u>                     |                           |           |     |  |

| k, publ   | Speed                              |                           |           |     |  |

| the wor   | Reliability                        |                           |           |     |  |

| title of  | Diagnostics                        |                           |           |     |  |

| rthor(s), | Local facilities                   | 000                       |           |     |  |

| the a     | Applications                       |                           |           |     |  |

| ution to  | Execution speed                    |                           |           |     |  |

| attrib    | Stability                          |                           |           |     |  |

| maintain  | Error reporting                    |                           | 000       |     |  |

| must      | Standardisation                    |                           |           |     |  |

| his work  | Flexibility                        |                           |           |     |  |

| tion of t | Ease of use                        |                           |           | 000 |  |

| distribu  | Key                                | The more blobs the better |           |     |  |

| ). Any    |                                    |                           | poor      |     |  |

| (© 1992   |                                    |                           | adequate  |     |  |

| ) licence |                                    |                           | good      |     |  |

| C BY 4.C  | 4.1 SPS old                        |                           |           |     |  |

| if the C  | SPS old SPS new LEP  Network Speed |                           |           |     |  |

### 4.1 SPS old

A key feature of the NODAL based control system is flexibility. It is extremely easy to produce a working application program, communicating with the machine and displaying data to the user. While this is an excellent feature, particularly for equipment testing or for one-off applications, as operations become more complicated it becomes more difficult to control the overall coherence of the system.

þe In the SPS the operational applications grew out of equipment commissioning programs, essentially on a system by system basis, and in an iterative way. As an example quadrupoles, 🌚 👷 Content from this work

sextupoles, octupoles etc were all controlled by different suites of programs all essentially doing the same thing. Adding a new system involved adding a new suite of programs to control it. Apart from the obvious problems of duplication of effort, this has also led to a certain diversity of the way similar functions had to be performed in different applications, which is very confusing to the user and makes it difficult to remember how to drive the different programs.

Because it is so easy to write or modify programs in this environment, in the absence of any real software management the stability of the applications is never fully achieved, and maintenance is consequently very difficult.

The very limited memory available in the control room consoles meant that most of the applications had to be kept small, and as a direct consequence of this error reporting had to be kept to a minimum, as did commenting the code.

Finally the speed at which the applications run has been found to be adequate. Since no online database exists the individual programs do their own data management, and though this brings its own problems it tends to be fast. Consequently the speed is determined by that of the NODAL interpretor and that of the TITN network. As a benchmark, sending a 100 point amplitude vs time function to the accelerator takes around 1 second per hardware address, which is considered acceptable.

### 4.2 SPS new

There were two significant differences between the way the new SPS applications were developed as compared to the old. Firstly the overall functionality of the software needed to operate the accelerator was analysed in detail before any design was considered, and secondly the underlying data structures were completely determined before any implementation was undertaken [4]. By its very nature this kind of software development leads to software that needs little change once implemented, and results in a very stable system. The highly modular way in which the applications were designed allowed an easy and standard way of handling errors, and the error reporting is excellent.

Knowing the detailed functionality led to a high uniformity, not just at the level of the operator interface [5] but more generally in the facilities the different applications shared. As examples there is only one function editor, one dataviewer and one application that is able to send to the equipment anything from a single function to the settings for the whole machine. This has contributed greatly to the ease of use of the software, and this is enhanced by a standard online help facility describing how to

drive the applications.

Having a sound definition of the data has allowed the applications to be largely data driven, giving coherence to the different accelerator systems and allowing new systems to be integrated without writing a single word of code.

The major disadvantage of this approach is that the software has been produced specifically to operate the SPS in the various modes forseen over the next ten years. Any novel running of the accelerator during machine development sessions invariably requires new features which are very difficult, sometimes impossible, to accomodate. Up to now these problems have been overcome by exploiting the high flexibility of the old TITN system.

The speed of execution of tasks is similar to the old system, but in this case database access times and the TITN network are the determining factors. The reliability of the gateway into the TITN is not good but problems are easy to spot and rectify.

### 4.3 LEP

Before the construction of LEP was complete, an analysis of the software required to run the machine was made. Naturally the emphasis was put on the software needed to commission the accelerator, and for the startup of LEP the controls and equipment groups provided a suite of powerful utilities for sending settings to and acquiring data from the hardware. These utilities exist as commands on the control room consoles and provide a means of quickly making script programs to do standard or non-standard things to the accelerator. Much use of this facility has been made during the commissioning phase, and more recently by accelerator physicists during machine development sessions.

The applications used today in operations also make heavy use these utilities for accessing the hardware. While this may be convenient for the programmers it invariably introduces overheads in the execution speed. The speed is further reduced by the underlying online data organisation, since the structuring of the data does not reflect the way in which we now want to run the machine.

The development of the operational applications has not followed an integrated approach, which has brought low coherence and a very variable level of error reporting.

Uniformity across the user interface applications has been achieved to some extent. Following the standards of the SPS has ensured a look and feel of the individual applications that is liked by the operators, and most programs are now easy to use.

The operational software relies heavily on servers running at all levels of the network, from the control room Apollos down to the front end computers. While communication between these servers is normally transparent to the user it often involves passing through several bridges. If one of the bridges or servers dies it is sometimes difficult to diagnose which one, and in many cases a procedure of sequentially restarting one after the other is required.

Furthermore many applications are dependant on certain computers to be up in order to run. There are presently around 10 such critical nodes on the control room token ring, the failure of any one of which would affect operations to some extent, in many cases seriously.

These two implementation details directly affect the overall stability of the software needed to run the machine.

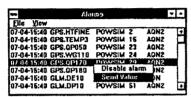

### 5. Alarms

Quite apart from the application software used to drive the accelerator, there is another area of the control system that is of great importance during routine operation of the machine, namely the surveillance system.

Ideally this should work on the simple principle that software, running without operator intervention, should check that all elements required to be ON are ON, that those that should be OFF are OFF, and that all settings stay within a tolerance acceptable for operations. This software, running frequently, should report any abnormal findings to an alarm system for processing prior to presentation to the operator as a new alarm on his screen [6].

In practice the viability of such a system depends very much on other parts of the control system. It is imperative for such a system to have available a definitive source of data reflecting the way the machine is actually supposed to run at the time. Furthermore because most machines run in several modes of operation, each requiring a different configuration, this image of the machine has to be dynamic.

It has already been mentioned that the LEP operational applications have not been developed in an integrated way, and one consequence of this is that there are several different ways of storing the actual machine settings. This makes it very difficult to provide standard surveillance programs; in reality each set of equipment has to have it's own program, a situation which is of course very difficult to administrate. So while for LEP the central alarm server works well, the amount of useful information reaching the operator is presently rather limited.

The same problems were encountered with the alarm system running on the SPS TITN network. Again there was no coherent image of the machine, and it took several years before the alarm system was providing information of sufficient credibility for the operators to use with confidence.

It is ironic that the new SPS operational software, which is driven from a central online database, does not yet have any kind of alarm system. Indeed we are experiencing problems due to this as more and more systems are migrated from the TITN to the 5 Apollo-based software, since there is presently no means of surveying them. The aim is eventually to use the same system that is presently in use for LEP, but with simple surveillance author( programs comparing measurements with settings in the online database.

### 6. Conclusions and remarks

attribution to the In the case of both the SPS and LEP, the network and control room utilities proved adequate during the running in of the machine. As testimony to this, beam was circulating in LEP one or two days after first injection, and the first Zo was reported within a month.

However, remember also that machine commissioning is done by specialists and over a limited period of time. When it comes to building the complex, integrated software packages that are required in routine operations, it has proved difficult to do so from the utilities provided. What is needed is a review of the operational requirements and a corresponding rewrite of the application software. Furthermore it is very difficult to determine these operational requirements in advance of getting hands-on experience of the accelerator.

🙉 🚇 Content from this work may be used under the terms of the CC BY 4.0 licence (© 1992) The new SPS software is a good example of what can be done. It was based on 10 years experience of running the SPS in a variety of modes, and the software produced satisfies most of the operational requirements.

The same thing now has to be done for LEP, this time after 3 years experience but drawing on the lessons learned in the SPS.

### 7. References

- [1] M.C. Crowley-Milling, "The Design of the Control System for the SPS", CERN 75-20

- [2] M.C. Crowley-Milling, "Experience with the Control System for the SPS", CERN 78-09

- [3] R. Rausch, "Real Time Control Networks for the LEP and SPS Accelerators", in Control Systems for Experimental Physics, Villars, Switzerland, September 1987, pp. 244-247.

- P.G.Innocenti, "The LEP Control System", in Accelerator and Large Experimental Physics Control Systems, Vancouver, Canada, 1989, pp 1-5

- P. Lienard, "The SPS and LEP Control Network Architaecture", in Accelerator and Large Experimental Physics Control Systems, Vancouver, Canada, 1989, pp 215-220.

- [4] R. Bailey, J. Ulander, I.T. Wilkie, "The New Applications Software for the CERN SPS", in Control Systems for Experimental Physics, Villars, Switzerland, September 1987, pp. 158-163

- [5] A. Ogle, J. Ulander, I.T. Wilkie, "Experience with Workstations for Accelerator Control at the CERN SPS", in Accelerator and Large Experimental Physics Control Systems, Vancouver, Canada, 1989, pp 437-441.

- [6] M. Tyrell, "The LEP Alarm System", these proceedings.

must

S. Schaller, R. Stuewe, E. Bjorklund, M. Burns, T. Callaway, G. Carr, S. Cohen, M. Harrington, D. Kubicek, R. Poore, and D. Schultz Los Alamos National Laboratory Los Alamos, New Mexico, 87545, USA

### Abstract

In recent years, control system efforts at LAMPF have emphasized the provision of uniform control for the LAMPF linear accelerator and associated beam lines and the Proton Storage Ring and its associated beam lines. The situation is complicated by the presence of several control philosophies in the operator interfaces, data base mechanisms, and front end data acquisition and control interfaces. This paper describes the current system configuration, including the distributed operator interfaces, the data and control sharing between systems, and the use of common accelerator diagnostic software tools. Successes as well as deficiencies of the present system will be discussed with an eye toward future developments. \*

### I. BACKGROUND

The Clinton P. Anderson Meson Physics Facility -- also known as LAMPF, the Los Alamos Meson Physics Facility -is composed of an 800 MeV proton linac plus associated beam lines and targets, and an 800 MeV Proton Storage Ring (PSR) plus its beam lines and a neutron spallation target that serves the Los Alamos Neutron Scattering Center (LANSCE). The linac accelerates beams of H+, H-, and polarized H- (referred to as P-) ions up to 120 times per second in pulses of up to 1000 microseconds width. The average H+ beam current can be as much as 1 mA. The proton storage ring serves as a beam compressor, taking a full H- macro-pulse from the linac and ejecting it in several hundred nanoseconds.

When LAMPF was built in the 1960's it was one of the first accelerators to be designed for computerized control. Since the IEEE CAMAC standard did not exist at that time, a significant amount of effort went into the design and construction of LAMPF-specific data acquisition hardware. The system that resulted was called RICE (Remote Instrumentation and Control Equipment). RICE hardware is still used for more that 60% of the linac equipment. Over the years, the control system was expanded to include CAMAC hardware accessed on demand through remote computers. With the addition of remote operator consoles, the initial star architecture has evolved into a much more distributed configuration.

The Proton Storage Ring was designed in the early 1980's to be independent of LAMPF with a separate control room and beam lines. As a consequence, the PSR Control System was designed and implemented with only minimal consideration of LAMPF requirements. The PSR system did provide recognition of its effect on linac timing requirements and it used a device naming scheme that was similar to LAMPF's. The PSR system emphasized continuous update of a centralized database.

In 1988, responsibility for the Proton Storage Ring was transferred to LAMPF. This paper describes the present configuration of the two control systems and the attempts that have been made to integrate them in a useful manner. We conclude with a brief description of our plans for the future. More information about our plans can be found in a companion paper at this conference [1].

### II. CURRENT CONFIGURATION

### A. LAMPF Control System (LCS)

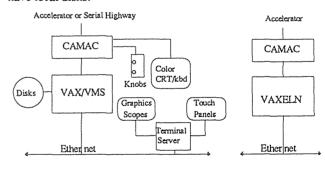

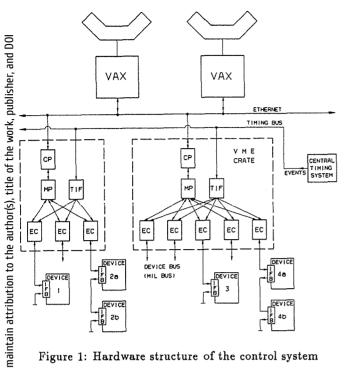

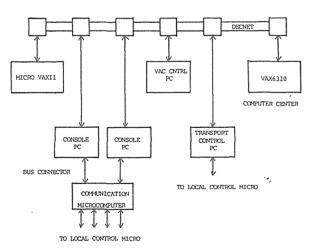

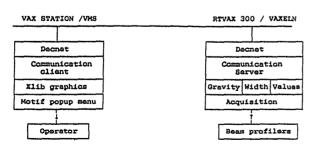

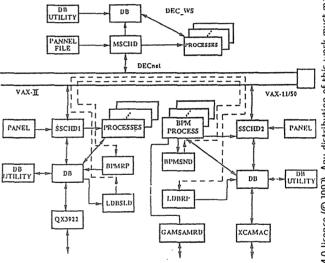

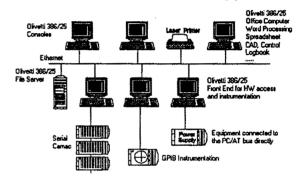

The evolution of the LAMPF Control System (LCS) has been described in detail elsewhere [2-4]. The LCS is currently composed of a network of VAX computers connected via an Ethernet using DECnet for communications. Computer Ethernet using DECnet for communications. Computer systems in the LCS network are of two types, (Figure 1). A typical LCS operator console computer runs VMS and drives one or more LCS operator consoles. Such a computer may also have a CAMAC-based data acquisition and control capacity. A typical LCS data acquisition front-end computer runs the VAXELN real-time kernel and handles hard real-time data acquisition through CAMAC. The VAXELN nodes do not have local disks.

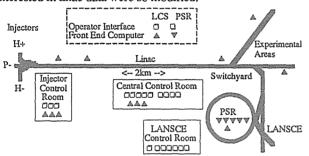

Figure 1. LAMPF Operator Interface and Front End Computers

Each LCS operator console is composed of one or more g color character-cell CRTs which are shared between a number of application programs, several graphics scopes, trackballbased touch panels, and a set of analog control knobs. The graphics scopes and touch panels are attached to the computer

**S01SRA02**

Content from this work

work, publisher, and DOI

must maintain attribution to the

used under the terms of the CC BY 4.0 licence (© 1992)

<sup>\*</sup> Work supported by the U.S. Department of Energy

through terminal servers. The color CRT and knobs are attached through CAMAC.

The color CRT in the LCS operator interface allows any LCS program to be called up at the operator's demand. This interface also gives the operator access to a number of supervisory tools which allow the state of any devices to be ∃ displayed and controlled. The touch panels also allow access to a fixed number of application programs.

LCS operator consoles are now supported in the LAMPF Central Control Room (CCR), the Injector Control Room E (ICR), and the LANSCE Control Room (LCR). (See Figure 4 for a geographic representation of this distributed # functionality.) The main CCR control computer was the center of the original star configuration. It still maintains its central position as it drives four of the five LCS operator consoles in CCR and serves as the central repository for LCS e software and databases.

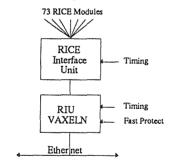

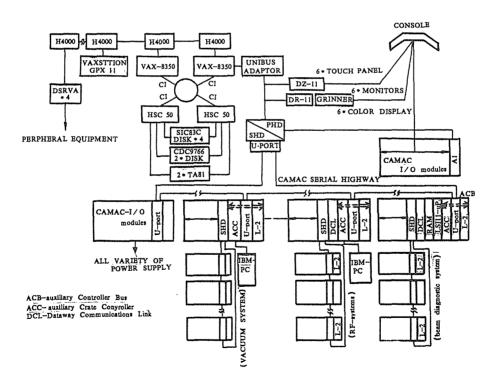

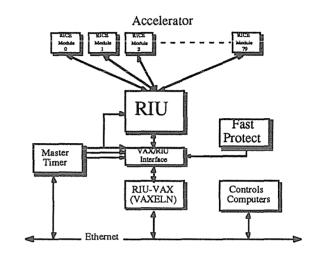

Since the RICE hardware was and still is a primary feature of the LAMPF Control System, a VAXELN front-end computer is dedicated as its interface with the rest of the control system (Figure 2). The RICE system is composed of 73 hardware data acquisition modules arrayed along the linac and in the injector and experimental areas. A distinct advantage of the RICE system is that it supports simultaneous timed data takes on each RICE modules. This provides a very powerful method for acquiring longitudinal snapshots of the entire linac at a particular time on a particular beam pulse. For untimed data takes, data caching facility is provided. In addition, the RICE system interfaces with the accelerator "fast protect" system. If a hardware monitor determines that too much beam is being spilled, the fast protect hardware sends a signal that simultaneously inhibits the injector and notifies the RIU computer that a fast protect has occurred. The RIU Ecomputer immediately reads the state of all hardware monitors To determine where the fast protect occurred.

Figure 2. LAMPF RICE Interface Front End Computer

LCS data acquisition is demand driven. Each node in the ELCS network contains a static database derived from a master Edatabase on the main CCR computer. Application programs Trequest data and issue commands through a standard data access interface which uses the local database to resolve device addresses at run-time. Application programs may be split up Eamong several nodes. A locally designed Remote Procedure ECall (RPC) interface allows the pieces to communicate without dealing with the complications of DECnet. Programs 🙃 👷 Content from this

that know they need large amounts of data can improve their system throughput by forming "aggregate devices." The LCS data access interface makes use of information supplied by the program to optimize network usage.

Because of the uniformity of data acquisition interfaces, if the correct application programs and databases are supplied to it, any LCS operator console on the network could run the entire accelerator.

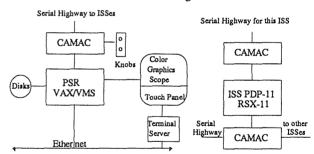

### B. PSR Control System

The PSR Control System attempts to achieve high data throughput and reasonable operator interface response by tightly coupling a central database to external computers that are continuously polling data. Detailed descriptions of this system have been published elsewhere [5-6].

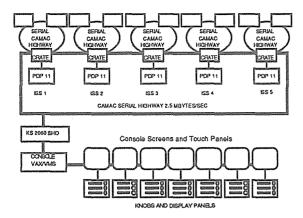

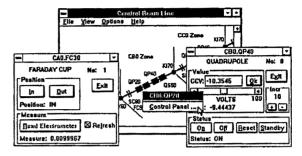

A diagram of the PSR operator interface and front end computers is given in Figure 3. All PSR operator consoles are attached to the PSR VAX. This machine serves as the operator interface computer and the central data concentrator. A typical PSR operator interface screen consists of a color graphics scope whose face is overlaid with a touch sensitive surface. The graphics scope is driven directly from the computer bus; the touch panel is driven through a terminal server on Ethernet. A set of analog control knobs is controlled via CAMAC. The top level screen on each color graphics scope provides an entry to a tree-structures menu of possible programs that can be started.

The PSR front-end computers are PDP-11s each connected to a CAMAC serial highway for data acquisition and control. These front-ends are know as Instrumentation Sub-Systems (ISSes). They continuously update their local databases with data from their serial highways. The ISSes are also connected to each other and the PSR VAX via a separate CAMAC serial highway over which the PSR VAX reads the latest data from the ISS databases and transfers changes in control values.

Figure 3. PSR Operator Interface and Front End Computers

Application programs running on the PSR VAX typically have exclusive access to a single graphics scope. The programs access data and set control values in the central database. They can also be notified asynchronously of changes in database values. Device data addresses in the central database are resolved at link time for many of the PSR application programs. This limits run-time overhead, but results in problems if the database structure changes.

of the CC BY 4.0 licence (© 1992).

### C. Control Systems Integration

When the Proton Storage Ring was first commissioned, it was controlled entirely from LCR. LAMPF at that time had operator consoles in CCR and ICR, although most operations activities took place in CCR.

The first attempt at LCS/PSR integration was to place PSR control consoles in CCR. Since we also wished to keep LCR available for PSR beam development, we had to pull cables between the two control rooms to physically connect the remote PSR consoles with the PSR VAX. At the same time a LCS console (CPU, color CRT, graphics scope, and knobs) was installed in LCR.

We then approached the more difficult job of sharing data and controls between the two systems [7]. By adding software (mainly run-time libraries and a copy of the LCS database) and LCS console hardware, we were able to make the PSR VAX into an LCS operator interface computer. This meant that PSR application programs could access LCS data through the LCS data interface. Several PSR applications that were interested in linac data were so modified.

Figure 4. Distributed Functionality in the LAMPF-PSR Network

The situation with LCS programs was a bit more difficult. Since only programs residing on the PSR VAX could access the PSR database, we added an LCS Data System server process to the PSR VAX. This process (which is a variant on the standard LCS Data System server) handles network requests for information on PSR devices. Since the LCS programs make standard requests for data, all the LCS programs, including the supervisory display and control tool, the LCS knobs, and the LCS data archiver could get PSR data.

Figure 4 show the geographic distribution of LCS and PSR consoles and front-end computers. This figure does not show details of CAMAC highways, Ethernet connections, RICE cabling, or timing distribution.

### III. EXPERIENCE

### A. Front Ends

The RICE hardware system presents some unique problems to the control system. Since more than 60% of the LCS hardware is attached through the RICE system and is only accessible through the RIU front-end computer, this represents

a major bottleneck. The fact that we have a limited amount of RICE hardware available means that we cannot easily expand the system.

The RICE interface can only perform one timed data take per beam pulse. This severely restricts tuning operations which are typically performed at low rep rates. We would like to improve on this performance even though we would like to keep the capability for doing synchronized timed data takes. Other RICE problems include not being able to send analog commands to more than one device in a RICE module at a time. This constraint creates problems when one is trying to scan wires in two wire scanners in the same RICE module.

The primary problem that we have found with the PSR ISSes is that of performance. The PSR equipment modules which reside in the ISSes are flexible and can acquire data rapidly. But the overall response is slow because data is scanned and transmitted regardless of its usefulness. The inherent flexibility becomes a problem because some modules 2 respond differently to the standard read and command requests 5 that are issued from the application programs. We need a carefully designed application program model of the world and disciplined equipment module implementations that ensure standard responses.

### B. Databases

A database system in an experimental installation must be able to add and change device definitions quickly without taking the control systems offline. The LCS database succeeds in this respect; the PSR database does not. After a PSR device 5 definition has been modified, it can take hours to regenerate a new PSR database. To be able to communicate with PSR devices, the LCS database must contain the PSR device names. This is possible because both systems use the same device naming scheme. Unfortunately, there is no automatic scheme for rationalizing the names that occur in the two databases. For now we use editors to compare lists of names to determine what should be a changed.

### C. Application Programs

The difference in design philosophies between the two control systems is most noticeable in the application programs. The absence of a notification on change in the LCS data access interface makes it hard to allow PSR programs to access LCS data through the PSR data access mechanism. As a compromise, we have made it possible for PSR programs to access LCS data through the LCS access mechanism. On the other hand, it was relatively easy to enable LCS programs to access (possibly old) PSR data. For application programs driving a future common LCS/PSR operator interface we should like to have data from both systems provided in a uniform manner.

### D. Operator Interfaces

Neither the LCS nor the PSR operator interface lend themselves to upgrade. The LCS technology is old and cannot integrate graphics and control functions. The PSR screens are becoming unmaintainable and cannot be moved to other nodes in the network because PSR applications need to access the central PSR database directly. The LCS supervisory tools allow operators to directly access any device. The PSR tools must be recompiled to allow access to new devices. We have found that the flexibility provided by the LCS interface is vital in running a basically experimental accelerator.

### E. Reliability and Maintainability

the Hardware reliability and maintainability has been a key issue during recent accelerator runs. The RICE hardware is getting old and becoming difficult to maintain. Replacement hardware is no longer being manufactured. While CAMAC hardware is available for replacements and additions, its use in harsh environments sometimes leads to short lifetimes.

The use of long serial CANAGE is the lifetimes.

The use of long serial CAMAC highways, especially in the PSR system, has led to difficulties in problem isolation. ĕ optic driver at a time from the highway in order to isolate a This can be a very time consuming operation, especially if it has to done during production.

We have also been concerned about single points of failure within the control system. As the systems stand now, the failure of a single LCS operator interface or front-end computer only means that the CAMAC attached to that machine is inaccessible. As mentioned above, with the correct data files and programs, any LCS operator interface computer in the network, including the PSR VAX, can run the accelerator.

The failure of the RIU front-end computer would be more serious for then we would loose all RICE data, a significant portion of the accelerator's data.

Loss of the PSR VAX would mean loss of the entire PSR system since the serial highway connections are only to that and the central PSR database resides on it.

### IV. THE FUTURE

the CC BY ь The concerns described in the previous sections are being Edealt with through several projects being currently planned or implemented at LAMPF. The projects and several other Econsiderations are described in detail in a companion paper at this conference [1]. In the remainder of this paper we will briefly summarize these projects.

At the lowest level, the front end data acquisition hardware At the lowest level, the front one will be upgraded to meet new requirements for reliability and maintainability. The plan is to use VAXELN-based micro-ZVAXes as the standard front end computer. These front ends will be used to replace the PDP-11s currently being used for the PSR ISS interface to CAMAC. At the same time, it is Eplanned to replace the RICE hardware with CAMAC and again

use VAXELN front ends. The effect of these two projects will be to unify all device access through a common client-server

A new common operator interface project has also been proposed. A common interface will reduce both training and maintenance requirements. We plan to use VAX-based workstations as the primary operator interface. We plan to use a user interface management system to keep the development and maintenance of the operator interface more manageable.

Since the new data access mechanism will not automatically put the data in the PSR database, existing PSR application programs may have to be changed. There is the possibility that some of these programs may be rewritten to make use of the new common operator interface. In the long run, this is what we hope to do with all application programs.

To improve the overall responsiveness of the control system, we hope to pursue several hardware upgrades beyond replacing the front end computers and introducing operator interface computers. Since, for a while, some application programs will still be using the old interfaces through the LCS and PSR central control computers, we hope to replace them with higher performance VAXes which can be clustered to provide hardware and file backup for each other.

With these upgrades we will be able to respond to increased demands on the LAMPF control systems in the future. Of most immediate interest are the controls necessary to support the proposed Pion Linear Accelerator (PILAC) to be built at one of LAMPF's beam lines. There are also proposals to upgrade the PSR from 100 to 300 µA to drive a possible pulsed lepton source, and to use LAMPF for prototype work in using an accelerator to transmute radioactive waste.

#### V. REFERENCES

- [1] R. Stuewe, S. Schaller, et. al., "Future Directions in Controlling the LAMPF-PSR Accelerator Complex," these

- [2] G. Carr, S. Schaller, et al., "The Status of the LAMPF Control System Upgrade," Proc. Europhysics Conference on Control Systems for Experimental Physics, CERN Yellow Report 90-08, (1990) p.107.

- [3] S. Schaller and E. Bjorklund, "Distributed Data Access in the LAMPF Control System," Proc. 1987 IEEE Particle Accelerator Conf., Washington, DC (IEEE Publishing, New York, 1987) p. 745

- [4] S. Brown, S. Schaller, et al., Proc. 2nd Int. Workshop on Accelerator Control systems (North-Holland, 1986) p. 122.

- [5] P. Clout, et al., ibid., 1986, p. 116.

- [6] P. Clount et al., "The Proton Storage Ring Control System," IEEE Trans. Nucl. Sci. NS-30 (1983) p. 2305.

- [7] S. Schaller, "Providing Common Data Access for the LAMPF and PSR Control Systems," Nucl. Instr. and Meth., A293 (1990) p. 416.

**S01SRA02**

© ♀ Content from

Accelerator and Fusion Research Division Lawrence Berkeley Laboratory University of California Berkeley, California 94720 U.S.A.

Abstract

This paper is a status report on the ADVANCED LIGHT SOURCE (ALS) control system. The current status, performance data, and future plans will be discussed. Manpower, scheduling, and costs issues are addressed.

### I. Introduction

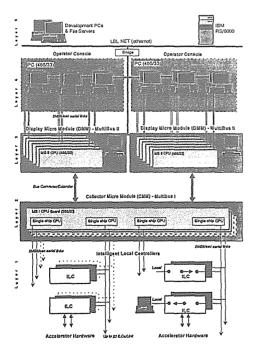

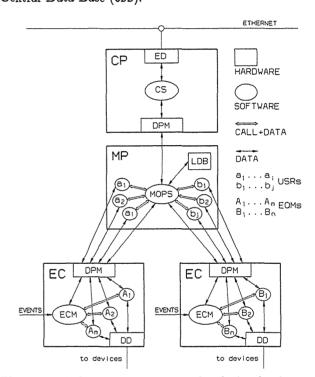

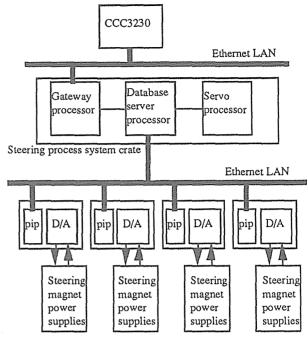

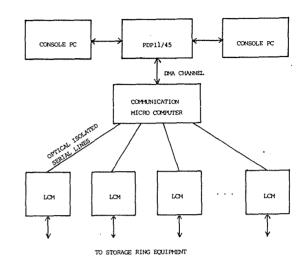

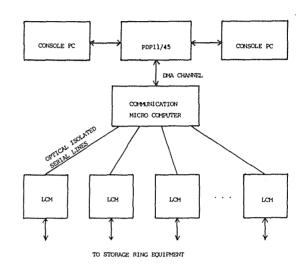

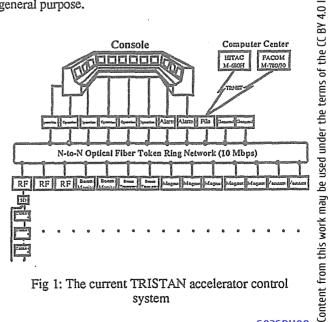

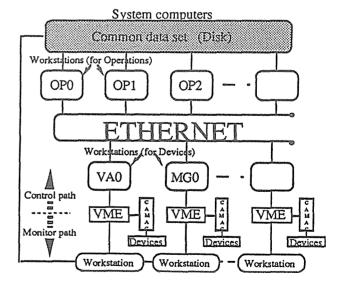

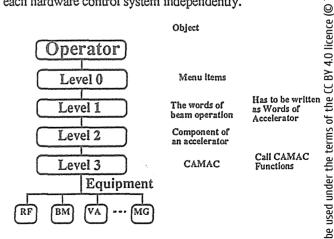

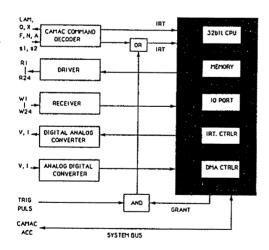

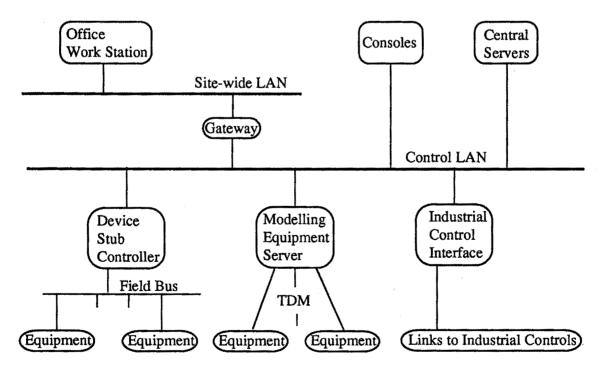

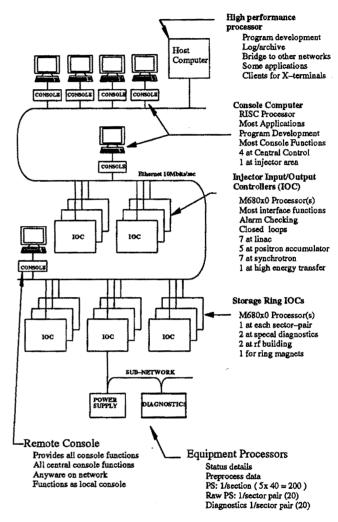

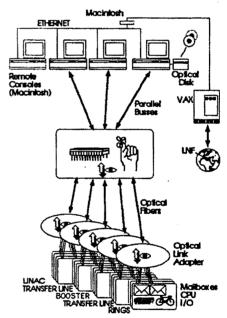

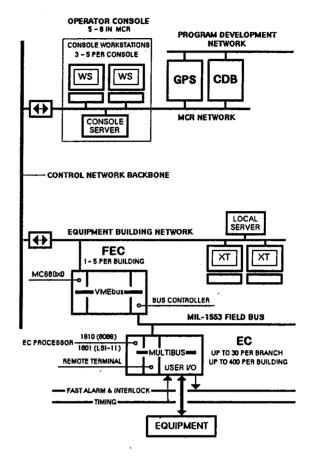

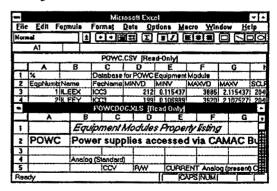

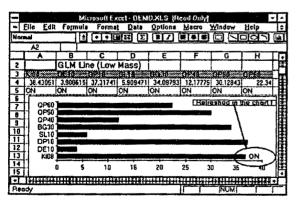

The ALS control system was designed around the concepts of parallel processing, high CPU and I/O bandwidth, and human-friendly interface. Figure 1 shows the system architecture and its five primary layers (for details of the system see References [1] and [2]). Layer 1, represented by the Intelligent Local Controllers (ILCs), interfaces to the accelerator hardware and communicates with Layer 2, the Collector Micro Module (CMM). Layer 3 is the Display Micro Modules (DMM) that has bus access to the CMM and in turn communicates with the operator stations (Layer 4) via serial links. The operator stations are high-performance Personal Computers that have Ethernet network (Layer 5) access to file servers and other network services.

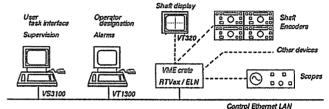

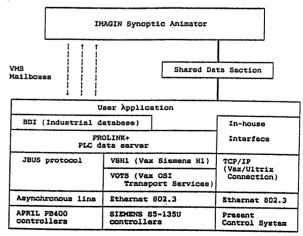

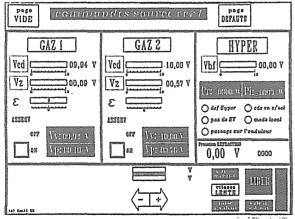

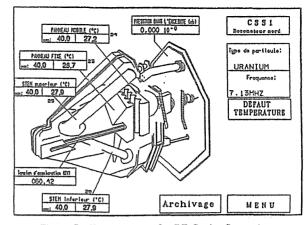

Figure 1. ALS control system architecture.

work, publisher, and DOI The ALS consists of an Electron Gun, a Linac, a Linac-to-Booster line, a Booster, a Booster-to-Storage-Ring line, a Storage Ring (SR), and a number of user beamlines. The control 5 system is currently operating the existing parts of the ALS accelerator hardware consisting of the Gun, Linac, Linac-to-Booster line, and the Booster; the Booster-to-Storage-Ring line is being implemented now. The Storage Ring accelerator hardware is under construction; completion is expected sometime during the second quarter of 1992. We will then be ready to begin commissioning the SR via the control system, both locally and from the Control Room. BY 4.0 licence (© 1992). Any distribution of this work must maintain attribution

Figure 2. Typical ILC installation.

### II. LAYER 1 (INTELLIGENT LOCAL CONTROLLERS)

The ILC is an intelligent controller consisting of an 80C186 main processor, an 80C187 math co-processor, and an 80C152 serial-control processor sharing 64 Kbytes of battery backed

memory. In addition, it has on board I/O resources of four 16bit DACs, four 13-bit ADCs, 24 bits of digital control, and an SBX bus for expansion. It is a low power (< 5 watts), 3U high Eurocard-based controller in a shielded metal can that can communicate at a 2 Mbit/sec rate using twisted pair cabling. We had commercial companies build 200 of these first generation ILCs. Twenty of them (10%) were not functioning when received from the manufacturer; ten had minor problems (chip leads bent, missing chips, infant mortality, etc.) and were repairable. The remaining ten we have not attempted to repair (they have missing traces or shorts on the circuit boards) since we decided the cost of repair was not justified. We are currently using about 140 ILCs in the accelerator, with an additional 20 to be used for the Booster-to-Storage-Ring line. See Figure 2 for a typical installation showing 3 ILCs, Opto-22 interface, and the 3 quadrupole power supplies. We expect to use an additional 500 ILCs to complete the project (Storage Ring, Beamline Front Ends), however, these will be the next generation design. These new ILCs will have 16 Mhz, 80C186EB chip as the main processor (a 60% speed improvement over the older ILCs'CPU, and also lower-power dissipation), 256 Kbytes of memory, 16bit ADCs and DACs, 16-bit SBX interface, a serial channel, and 28 Boolean lines. The analog and digital design is completed; layout and prototyping/testing will start shortly. The cost of the current ILCs is \$650 each; the new ones will be about \$950. To exercise the ILCs, and test the accelerator hardware, we use laptop computers (80386/80486-based), connected directly to the ILCs, using much of the same software as we use on the operating stations in the Control Room.

of the

Any distribution of this work

4.0 licence (© 1992).

B∕

Figure 3. DMM, CMM, fiber optic interface, and file server.

### III. LAYER 2. (COLLECTOR MICRO MODULE)

terms of the The CMM (Figure 3) contains all the data gathered from all # the ILCs (i.e., it represents the entire accelerator database at any moment). The ILCs are connected to the CMM via fiber-optic lines. The serial communication on these lines is bi-directional (though using only a single fiber), and the bit rate is 2 Mbit/sec. (though using only a single liber), and total I/O physical We are currently using 12 of these lines for a total I/O physical 当 bandwidth of 24 Mbit/sec. We use a commercial (Intel) 20 MHz, ₹386-based Multibus I board with 4 single chip processors (via custom built SBX modules) to service 4 serial lines. Therefore, to service the 12 lines currently in use, 3 Multibus I processors

are required. These boards allow us to handle approximately 800 messages, of about 75 bytes each, per second per line. Therefore, the total I/O bandwidth currently coming into the CMM is approximately 720 Kbytes/sec (12 x 800 x 75). This represents, on the average, about a 10 refresh/sec of the entire active part of the current accelerator database. We are currently evaluating a 33 MHz, 486 Multibus I board and are designing a new SBX interface that would allow us to service 8 lines per Multibus board at about 1600 messages/line/sec. At project completion, we plan to have approximately 64 lines (using 8 Multibus I processors operating in parallel) for a total I/O bandwidth of 128 Mbits/sec, and a useful data rate 7.5 MBytes/sec. This would represent, on the average, about a 15 to 20 per second refresh rate of the active database of the entire accelerator. We are also exploring the possibility of a second CMM; this would double our I/O bandwidth to 240 Mbit/sec at a modest cost.

### IV. LAYER 3. (DISPLAY MICRO MODULE)

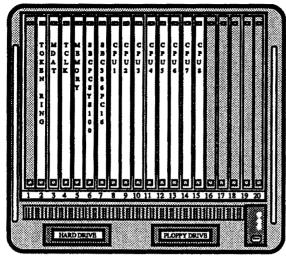

The DMM (Figure 3) consists of a 20-slot Multibus II System, bought as a unit from Intel Corp., that has fast parallel access (via a bus converter) to the CMM. This system contains a SCSI disc controller, an Ethernet interface, and a number of high performance singleboard computers. Under current operation, we are using 2 DMMs (we had not planned to install the second DMM till Storage Ring commissioning, so we are ahead of schedule in this area) to access the database in the CMM. The DMMs currently use RMX II as the real-time operating system (we are evaluating using RMX III, a full 32-bit system) using standard Intel hardware and software. The first DMM currently supports 6 (we have tried 7) commercial (Intel) 25 MHz, 486-cpu boards, while the second DMM currently uses 3 CPUs. The CPUs within each DMM operate in parallel, and each has 2 serial links (we promised 1, so this doubles I/O performance in this area) that directly connects it to the operator station. Each of these links has the same configuration as the links between the ILCs and the CMM (i.e., 2 Mbit/sec). At project completion, we will support at least 6 operator stations per DMM, for a total of 12 or more for the whole accelerator. We have enough bus bandwidth in the CMM so we could support even a third DMM. We plan to upgrade the CPUs in the DMM with processors that will be at least 2.5 times a fast as the current

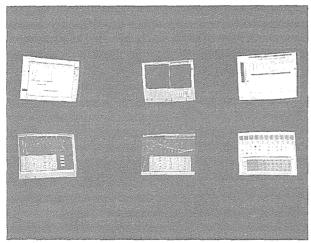

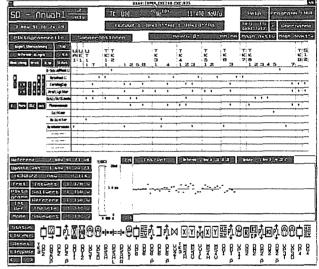

### V. Layer 4. (Operator Stations)

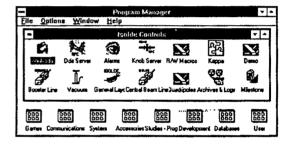

The operator station is the human interface of the Control System; it presents accelerator data, including real-time data, scope traces, and live video (via multi-media programs and hardware) to the operator. The operator can use mice, keyboards, or nine dynamically assignable/labeled knobs. Six operator stations make up a console (Figure 4), and each console is supported by one DMM. The operator stations use 33 MHz, 486-based AST Personal Computers (PC), but they are upgradeable to faster CPUs via a simple card swap. Most use Windows 3.0 as the operating system, a few use OS/21.2. The serial communication links to the DMM allow us about 800-1000 database accesses/sec for each PC in the database client/ server "request" mode. In the "driven" (i.e., when the DMM drives the PC) we can achieve about 1500 messages/sec. Both

© © Content from this

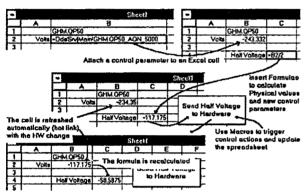

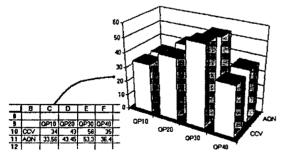

of these rates are CPU limited, we expect them to be about 2500 and 3000 messages/sec (at those rates we will be I/O limited) respectively at project completion. Since we plan to have at least 12 operator stations, we will attain accesses in excess of 30,000/sec; however, even at these rates, we are using only about 10% of the bus and data bandwidth available in the CMM-DMM combination. These facts demonstrate the very high performance available in our star-based, shared memory approach to control system design. The choice of the PC as our human interface has proved to be a judicious one. As the popularity of Windows grows, the availability of commercial software for use in the control system grows rapidly. We currently make extensive use of DESIGNER (graphic editing tool), EXCEL (spread-sheet), TOOLBOOK (HyperCard-like package), VISUAL BASIC, TURBO PASCAL for WINDOWS, as well as the usual languages C, C++, etc. With these PCs, we also have available the usual collection of word processors, databases, and utilities (screen capture, etc.). The use of this commercial software has greatly increased our productivity, and has allowed us to keep our staffing requirements very low. The one area where we need improvement is in support of full 32-bit modeling applications. These are currently done on workstations and can access the database via Remote Procedure Calls (RPC). We plan to shift this work to OS/2-2.0, or its equivalent, as soon as possible. In the meantime, X-Windowsbased applications can appear as a window on the PCs under Windows 3.0 or OS/2, using commercial software.

Figure 4. Operator console with six operator stations.

### VI. LAYER 5. (NETWORK)

The PCs are networked via Ethernet to a Laboratory-wide network. This allows workstations, etc., to access the database via RPCs. An IBM RS6000 Workstation is used by the physicists for modeling and 32-bit numeric intensive applications. We also have a PC on this network with a 600-Mbyte disk as a file server for the operator stations and software development. A spare server is available to minimize down-time in case of failure by the main server. This network will also be the "user" interface into the control system for wiggler/undulator and beamline front end controls. A protection scheme to limit user control, to specified devices only, is under development.

### A. Scheduling and Costs.

The control system is being used to commission the accelerator as it is being built. We are on target both in terms of cost and schedules, and are beginning to shift over to pre-operation. The staffing to date has been exactly as projected (with five programmers, one coordinator, and one half of an electronic designer) over the length of the construction project. Cost to date is approximately \$3.65M of a total projected cost of \$5M. Storage Ring commissioning is scheduled for the 2nd quarter of 1992, with project completion in 1993.

### VII. ACKNOWLEDGMENT.

This work was supported by the Director, Office of Energy Research, Office of Basic Energy Sciences, Materials Sciences Division of the U.S. Department of Energy, under Contract No. DE-AC03-76SF00098

### VIII. REFERENCES.

- [1] Magyary et al., "Advanced Light Source Control System," Lawrence Berkeley Laboratory, LBL 26028 and Proc. 1989 IEEE Particle Accelerator Conf., Chicago (IEEE Publishing, New York, 1989).

- [2] Magyary et al., "The Advanced Light Source Control System," Nuclear Instruments and Methods in Physics Research, A293 (1990) 36-43, North Holland.

# LESSONS FROM THE SLC FOR FUTURE LC CONTROL SYSTEMS\*

### Rusty Humphrey

Stanford Linear Accelerator Center, Stanford University, Stanford, CA 94309

work, publisher, and DOI The SLC control system is the dynamic result of a number of forces. The most obvious force is the functional requirements of the SLC itself, but other forces are history, budget, people, available technology, etc. The plan of this paper is to describe the critical functional Frequirements of the SLC which caused significant devel-popment of the control system. I have tried to focus on functional requirements as a driver, and I will describe negative solutions which we have implemented to satisfy Sthose requirements.

Sthose requirements.

The important functional requirements of the control system discussed in this paper are:

Repetition rate

Sensitivity to orbit distortion

Stability/Automation

Accelerator Development

REPETITION RATE

The SLC runs for physics production at 60 The important functional requirements drivers for

The SLC runs for physics production at 60 or 120 Hz.  $^{\circ}$ At 120 Hz,  $5 \times 10^{10}$  particles per bunch, 3 bunches/beam Epulse, and 50 GeV, the average power is 150 kW. If the Ebeam has a small enough cross sectional area, such a beam has caused damage to beam vacuum pipes, beam avacuum flanges, collimators, or other beam line compo-Inents by heating. Such events occur because the beam Shas become "errant"; that is, it has wandered from its nominal orbit, and is actually striking the device. If this situation is not detected, then more and more energy is Fput into the device, as the SLC pulses keep coming. The inrst issue is to detect the event, and turn off the beam. There are a number of classic methods of such detection SLC uses them.

Once the event is detected, how does one fix the problem? Usually the answer is to steer or tune the Emachine. But now a situation, which appears as a form of "relaxation oscillator," happens. To tune the beam, one Enceds beam in the machine. But because the beam is mistuned, the machine protection system detects the same Sproblem again and turns off the beam again. How does Sone break this impasse?

The first, and obvious answer is to tune at a lower beam intensity; instead of running with  $5 \times 10^{10}$  particles, tune with  $2 \times 10^{10}$ . This doesn't work in general. The SLC

Work supported by Department of Energy contract DE-AC03-76SF00515.

S01SRA04

with 2 × 10<sup>10</sup> particles is a sufficiently different machine from the SLC with  $5 \times 10^{10}$  particles that the problem often disappears at 2 × 10<sup>10</sup>, only to reappear when the current is raised to  $5 \times 10^{10}$ .

The next answer is to tune at the same beam pulse intensity, but to lower the repetition rate. This is, in fact the technique that is used at the SLC. However, it does not work to simply lower the repetition rate of all components in the machine to 10 or even 1 Hz. Power is dissipated in the rf and pulsed magnet systems, and lowering the repetition rate in such components changes their characteristics. Therefore, an effective rate limiting strategy requires that the rate of running the pulsed components of the machine not be changed, but that only the injection of electrons and positrons be moved to the lower rate.

The above discussion is an overview of the simplest situation; and even it isn't really simple—how the creation and injection of positrons is handled is problematic even in this situation. More complicated scenarios are also possible in the SLC [1].

Another issue for the Machine Protection System is configuration flexibility. As the SLC configuration is changed during tuning or machine studies, the requirements on machine protection change. An obvious example is a repetition rate change from 60 to 120 Hz. A less obvious example is changing the place where the beam is stopped. It is a requirement of the machine protection system that it react to such configuration changes in as seamless a manner and as prompt as possible. At the SLC, this functionality is provided by means of the timing system, which includes distribution of timing "patterns" which allow pulse to pulse timing configuration changes. This functionality is being augmented because it is required by a project to upgrade our present Machine Protection System [2], and because it is needed for the next phase of our Fast Feedback system.

To summarize the functional requirements: The repetition rate for a linear collider can allow errant beam to damage or destroy beam line components. A protection scheme is required which detects such situations, which limits the beam, and which allows retuning of the machine to stop the situation. It is required that retuning be done at or near the beam conditions which cause the errant beam. In addition, the machine and its machine protection system must be easily and quickly reconfigurable.

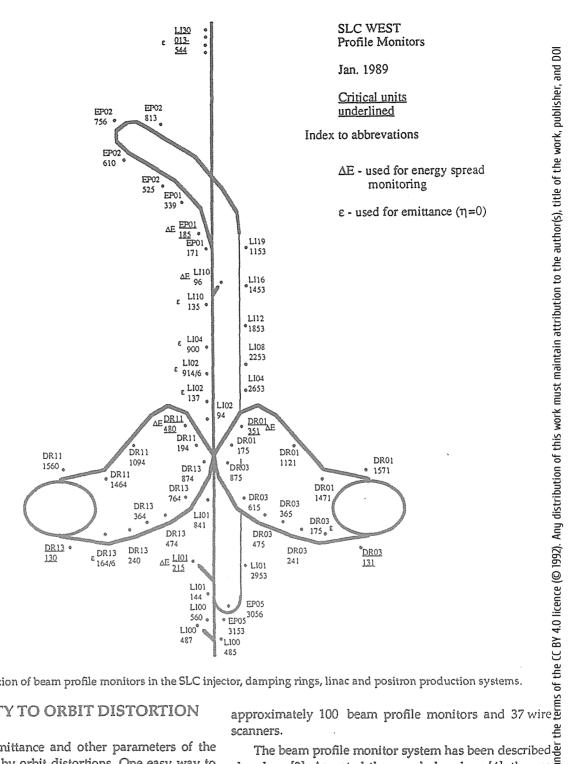

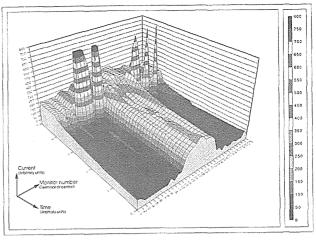

Figure 1. Location of beam profile monitors in the SLC injector, damping rings, linac and positron production systems.

### SENSITIVITY TO ORBIT DISTORTION

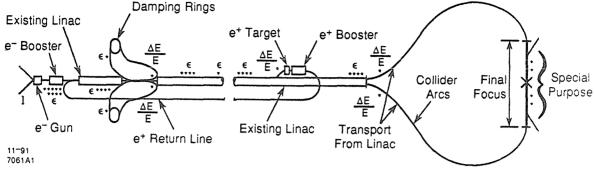

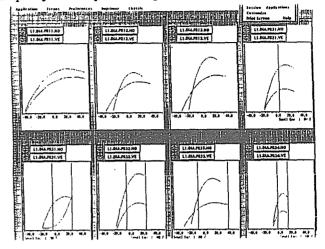

In the SLC, emittance and other parameters of the beam are affected by orbit distortions. One easy way to understand this is to remember that wake field tails are caused by off axis beams in the linac's disk loaded wave guide. As a result of this sensitivity, the mix of beam diagnostic systems required for the SLC is affected. Diagnostics which measure beam shape, beam size, and emittance are many. As shown in Figures 1 and 2, there are

scanners.

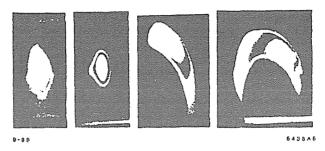

The beam profile monitor system has been described ਵੋ elsewhere [3]. As noted there and elsewhere [4], the use 5 of profile monitors is destructive to the beam, but they allow shape changes to be observed in real time and give g detailed information of transverse tail formation. (See # Figure 3.) In concert with an adjustable upstream quadrupole, beam profile monitors can be used to measure emittance [5].

Figure 2. Location of wire scanners in the SLC.

must maintain attribution to the author(s), title of the work, publisher, and DOI Figure 3. Images of an electron bunch on a profile monitor at 47 GeV showing wakefield growth with increasing specialistion amplitudes. The images from left to right are for a well-steered beam, a 0.2 mm oscillation, 0.5 mm oscillation. intion and a 1.0 mm oscillation, respectively. The beam intensity is  $2 \times 10^{10}$  electrons. The core sizes  $\sigma_x$  and  $\sigma_y$  are about  $\frac{1}{2}$ 120 mm. ð

The wire scanners have been alscussed Eelsewhere [6]. The beauty of wire scanners is that they Eallow nondestructive measurement of the beam emitand thus could be used as an online device in, for have not yet done example, beam feedback systems (we have not yet done so).

9 John Seeman has pointed out the need for what he Ecalls "corroborating measurements." As an example of what this term means, consider the fact that emittance Scan be measured by both profile monitors and wire scan-≥ners. The presence of two techniques allows the results Gof such measurements to be compared. If the measurements are equivalent, then they corroborate (or confirm) Sone another. This increases the credibility of the results— Ean important factor in a prototype accelerator.

Beam position monitors (BPMs) used in the SLC Enumber approximately 1700. All the BPMs in the linac ভা়tself are instrumented for single pulse data acquisition; Severy BPM so instrumented can be read out, under con-Etrol of the timing system, on any given pulse for a particgular beam bunch. BPM systems in the SLC arcs and in the adamping rings have multiple BPMs which are multi-Eplexed into a common data acquisition module; this prescludes reading all the BPM inputs into one of these modules on the same beam pulse. However, over the past year, we have had a couple of projects to "demultiplex" BPMs; that is, to instrument more BPMs in the same way as the linac BPMs so that orbit measures on a single beam pulse can be done. The builders of future linear colliders need to look carefully at the requirements for single pulse orbit measurement.

The impact of these beam diagnostic systems on the control system is large. Fundamentally, the data acquisition requirements for a linear collider correspond to that of the "first turn" for a circular collider. The ability to take a single pulse "snapshot" of the orbit, or a snapshot of many parameters associated with the beam or with individual pulsed devices is a requirement. As the references detail, emittance and beam shape measurements require sophisticated image processing and accelerator matrix manipulation and fitting. As the maps of profile monitors and wire scanners show, and as the number of BPMs implies, these systems are everywhere, and time spent on generalization and sophistication is well spent.

To restate the functional requirement: linear collider operation requires careful attention to diagnostics which measure beam orbit position and distortion, emittance, and beam shape.

© © Content from this

### STABILITY, AUTOMATION

The SLC is a large complicated device. Stability of the SLC is a large problem. Feedback systems, in which the control computer system is an active component of the feedback loop, have been operational at the SLC since 1988. Feedback based on signals derived from beam diagnostic instrumentation allows a much higher degree of control over the beams, since these data can be acquired from many sources and statistically fit. Single device tolerances could never provide this level of stability. The main application of these feedback systems is steering (launch angle and position); but feedback systems to correct energy, energy spread, and collision point are also used.

The earliest version of these was "slow feedback," with update times measured in tens of seconds; such loops are closed through the VAX mainframe which is the highest hierarchical level in the SLC control system. This was quickly augmented by prototype pulse-to-pulse feedback ("fast feedback") systems using a dedicated microprocessor based system, instrumentation, and controlled steering supplies. This prototype system was a very successful, but could only be replicated with difficulty and was difficult to maintain. We have since generalized this prototype and integrated it into the SLC control system. That generalization is propagating at a rapid rate to a large number of installations in the SLC, replacing both the prototype version of itself as well as many of the older "slow feedback" applications. This system is described in another paper being presented to this conference [7].

One of the major benefits of these fast feedback systems is the step forward in automation that they allow for accelerator operations. As described elsewhere [8], the SLC control system logs a number of different events on a continuing basis. One such class of events logged is "knob turns"; i.e., each time an operator turns a software-defined knob, that event is logged. As a result, we know that fast feedback has decreased the required intervention of operators to do knob turns by as much as 80%; fast feedback is doing the knob turning for us.

### ACCELERATOR DEVELOPMENT

The SLC is the prototype for a linear collider. The SLAC staff is working to understand how a linear collider works. One of the SLC accelerator physicists has noted that "...there are more interesting accelerator physics tests being proposed each day than there is accelerator time to perform them" [4]. The environment is such that there are numerous questions to be answered and there is often the need find answers quickly so that the answers can be incorporated into operation. It is an essential functional requirement that the control system supply

tools that allow the staff to do machine physics experiments which have never before been even considered.

The major tool—actually a set of tools—for this is the Correlation Plot Facility, described in a poster session \( \) paper of this conference [9]. This powerful software provides a set of tools for realtime online analysis, fitting, 5 plotting, control and measurement of a large number of variables. The facility is well integrated into the SLC control system, and programs or functions which are developed for physics studies are often incorporated into 끝 operational software [10].

This functional requirement will exist for the next # to the author(s), tii linear collider, since it will be built on an experience base of one-the SLC.

### COMMENTS

The control system for an accelerator must satisfy many functional requirements—many more than the four described above. These four were described because SLAC's experience shows that they are, in some way, = unique to the class of linear colliders.

There are other functional requirements which are common to all accelerators. And there are functional \square requirements which are unique to the SLC-a prototype linear collider based on the existing SLAC linac. Neither 5 of these classes of functional requirements have been discussed, although some of the solutions described above = help to meet them.

The four functional requirements described above have been a challenge which has been met by a large team of highly committed people. Some of that team is E named in the references, but there are many, many more. I would like to thank Marty Breidenbach, Ewan Paterson, Nan Phinney, Marc Ross, John Seeman, and John & Sheppard for recent discussions on this topic. licence (©

### REFERENCES

- [1] For a further discussion, see M. Ross, "Machine Pro-≧ tection Schemes for the SLC," 1991 Particle Accelerator Conference.

- D. Hutchinson, E A. Grillo, N. Spencer, [2] S. Clark, J. Olsen, D. Millsom, G. White, S. Allison, K. Underwood, M. Zelazny, and H. Kang, 🛱 "Smart Machine Protection System," Proceedings of the International Conference on Accelerator and Large Experimental Physics Control Systems.

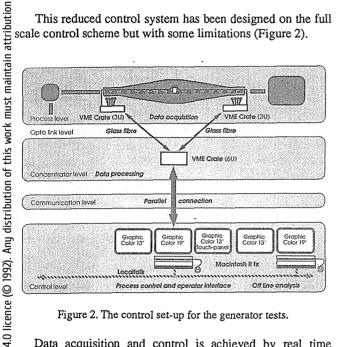

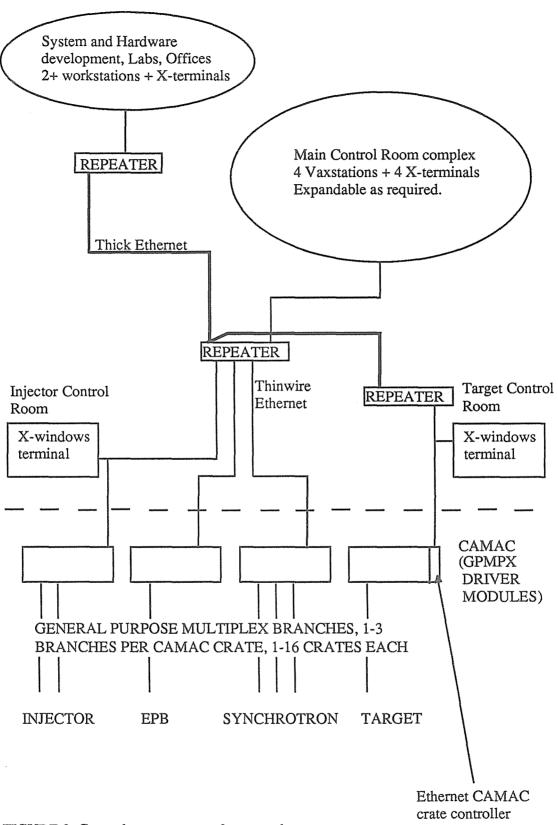

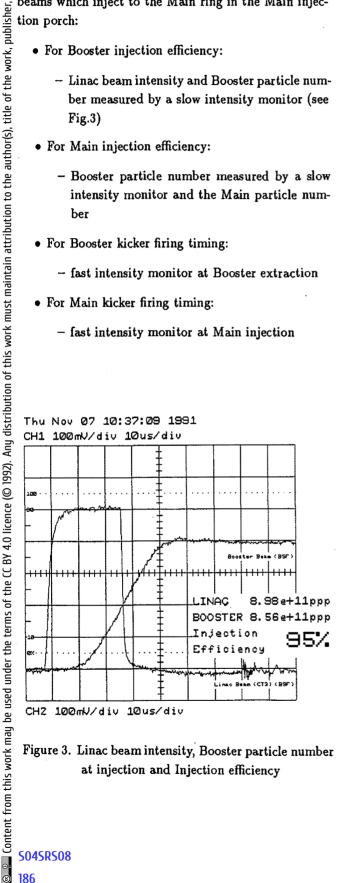

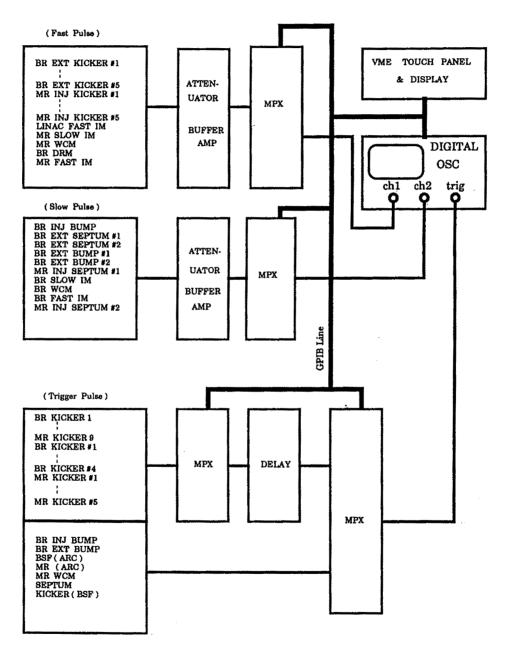

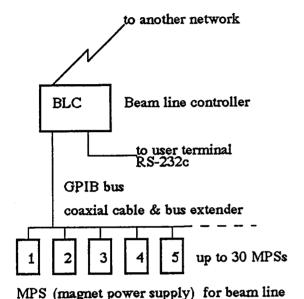

- [3] M. C. Ross, "Beam Diagnostics and Control for SLC 1987 Particle Accelerator Conference.